Israel-based Weebit Nano, founded in 2015, is addressing the memory market with innovative solutions. The company turned to the CEA to develop a complete demonstrator to promote its patented eNVM (embedded non-volatile memory) technology. Weebit Nano has already used the demonstrator to sell or license its technology to foundries in the US and Asia. The CEA’s knowledge of eNVM, circuit and systems design, and wafer- and package-level testing was what originally motivated Weebit Nano to explore the potential for a partnership.

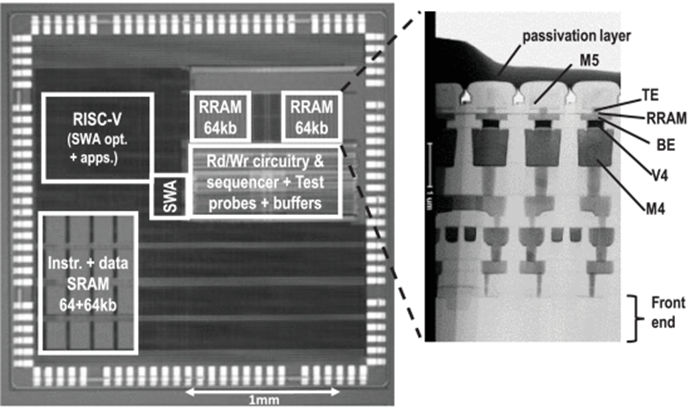

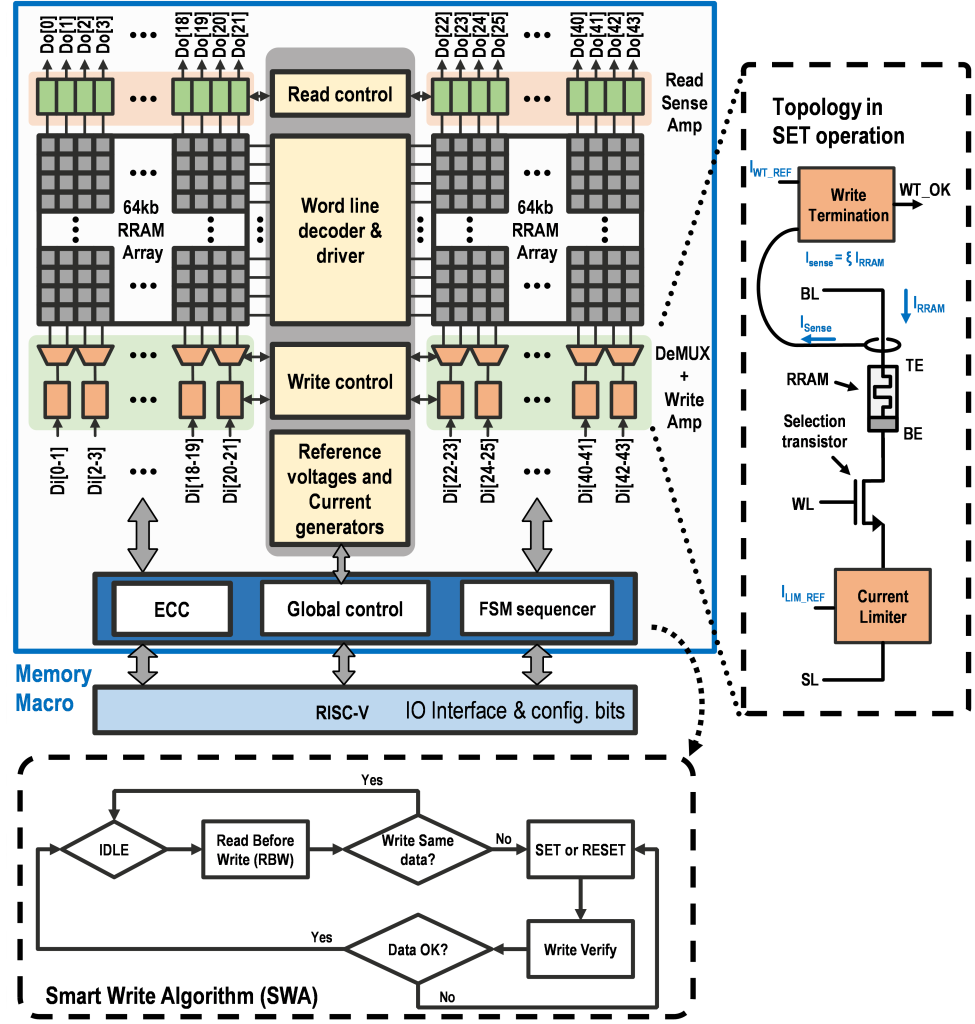

The demonstrator produced includes a non-volatile ReRAM macro and analog circuits that provide the precise, yet tunable signals required for this type of memory’s complex read and write operations (Figure 1). It also includes control circuits based on RISC-V subsystems, as well as a dedicated controller developed specifically for this project.

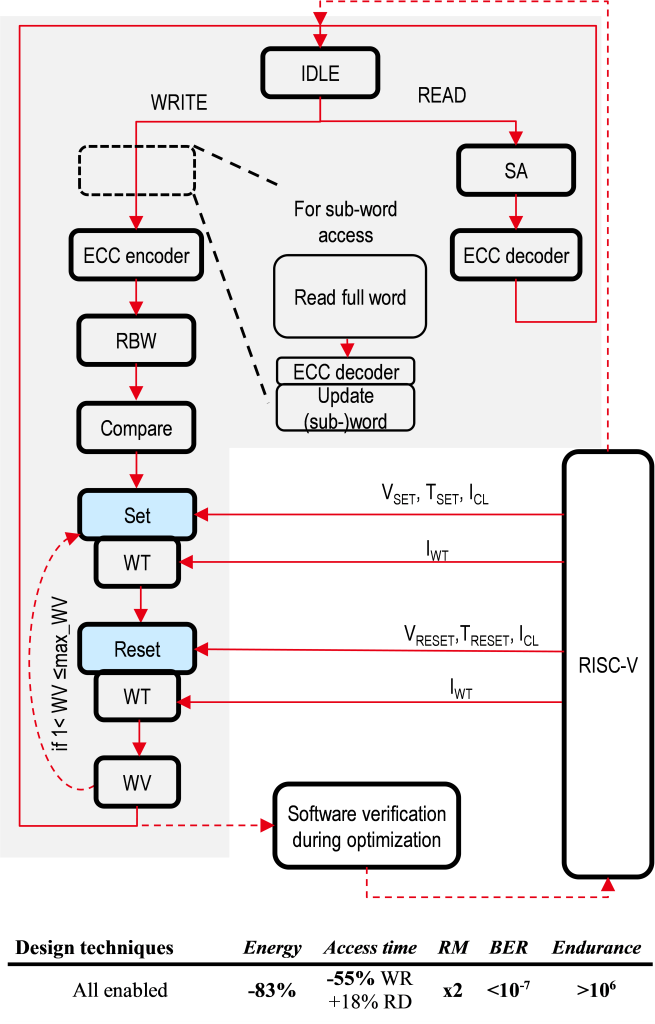

* Reading the binary value of a memory cell before each write operation and writing only if the bit is not in the desired state.

* Checking the state of the cell after the write operation and repeating the write operation until it is correct.

* An error correction code (ECC) that detects and/or corrects a word read using bits encoding the parity of the word’s subgroups.

This research and, especially, the optimizations obtained by using the Smart Write Algorithm, SWA, led to significant improvements (Figures 2 and main) at room temperature:

These improvements make the ReRAM technology developed with Weebit Nano a promising candidate for widespread industrial deployment.

This exciting project, which produced the CEA’s first NVM design, involved seven CEA laboratories from technology to circuit design to system-on-chip testing.

We are extremely happy with the team’s work... Meeting the schedule for the tapeout, adapting to Weebit change requests, implementing multiple test-modes and flexible design, extremely clean layout.

15x improvement in energy-delay product.