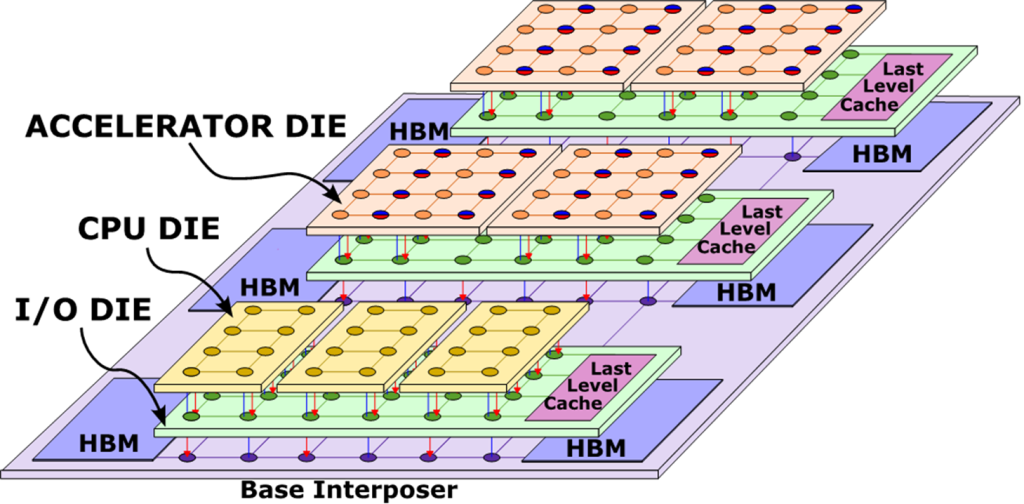

3.5D (also referred to as 5.5D) integration is revolutionizing circuit architectures: Instead of expanding chips horizontally, multiple chiplets are stacked on an interposer, in vertical miniature skyscrapers. Networks-on-chip (NoCs) with special routing algorithms allow flits (small units of data) to travel from a source to a destination, ensuring communication between the chiplets (processors, GPUs, accelerators…) in the stack. The routing algorithms used in 2.5D systems (in which several chiplets are stacked directly on an interposer) are well established. However, in 3.5D

architectures, flits can take several vertical routes between chiplets to reach their destinations, introducing additional complexity that requires innovative solutions. Fulbright Scholar Davy Million developed the Depth-First[2] algorithm specifically for 3.5D architectures as part of his PhD

research in conjunction with the University of California at Santa Barbara. The algorithm routes data efficiently, avoiding deadlocks (circular dependencies between network resources that can cause the network to stop functioning), marking a major advance for 3.5D circuits.

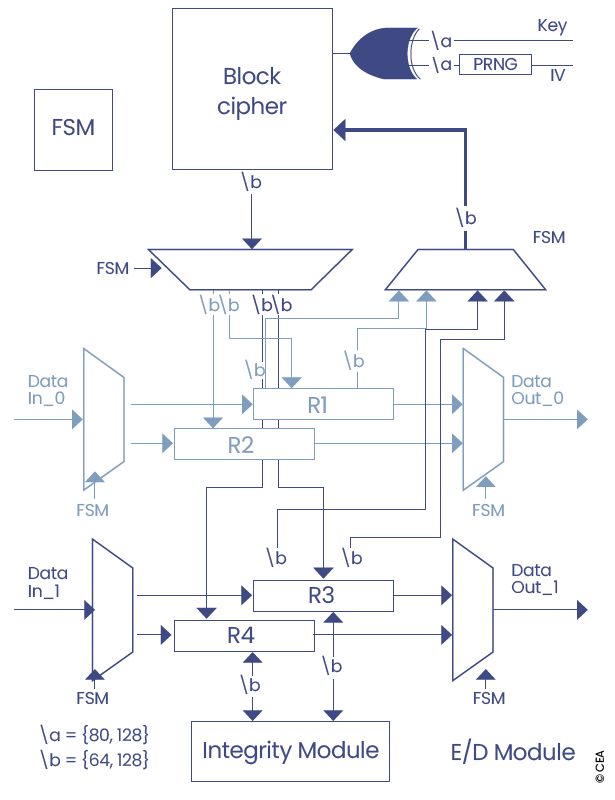

Multi-chiplet systems come out of complex and fragmented ecosystems involving chiplets manufactured by different foundries and then tested and assembled by other third-party companies. Despite this complexity, each chiplet must be authenticated to prevent counterfeit or malicious chiplets from being integrated into systems and to ensure that sensitive data cannot be exfiltrated through test ports. PhD student Juan Suzano’s research, financed by STMicroelectronics and conducted in partnership with STMicroelectronics and TIMA (a Grenoble INP-Grenoble Alpes University-CNRS joint research unit), resulted in an innovative solution combining chiplet authentication and test data encryption. The solution

developed, compatible with IEEE standards 1686 and 1838 and designed for industrial deployment, was published in JETCAS[3]. This concrete response to the vulnerabilities of chiplet-based architectures will support the development of an open, secure ecosystem.

"3D integration is now a pillar of highperformance system architectures.»

The market for chiplets and 3D

circuits is expanding at a 24%

CAGR and is expected to reach

$157 billion by 2030.

3.5D NoC simulator on CEA-List’s GitHub: https://github.com/CEA-LIST/Noxim-3.5D

[1] P. Vivet et al., “IntAct: A 96-Core Processor With Six Chiplets 3D-Stacked on an Active Interposer With Distributed Interconnects and Integrated Power Management“, in IEEE JSSC, vol. 56, no. 1, pp. 79-97, Jan. 2021. (https://doi.org/10.1109/JSSC.2020.3036341)

[2] D. Million et al., “Depth-First: A Deterministic and Scalable NoC Routing Protocol for 3.5D Packaged Architectures“, IEEE JETCAS 2025. (https://doi.org/10.1109/JETCAS.2025.3590106)

[3] J. Suzano, et al, “Enhancing DFT Security in Chiplet-Based Systems With Encryption and Integrity Checking“, in IEEE JETCAS 2025. (https://doi.org/10.1109/JETCAS.2025.3592984)