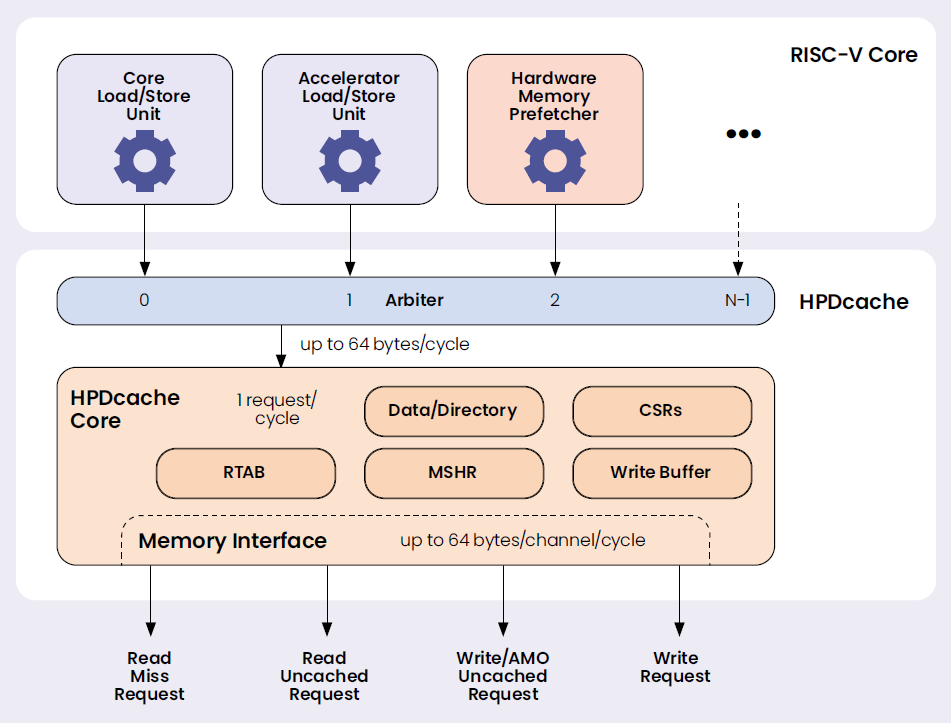

HPC and AI applications are increasingly data intensive. Plus, their memory access patterns are irregular, making the cache memory less efficient—a major barrier to improved performance. HPDcache, which allows multiple memory requests to be executed simultaneously, solves this problem, masking memory access latency and providing high bandwidth, for better overall system performance.

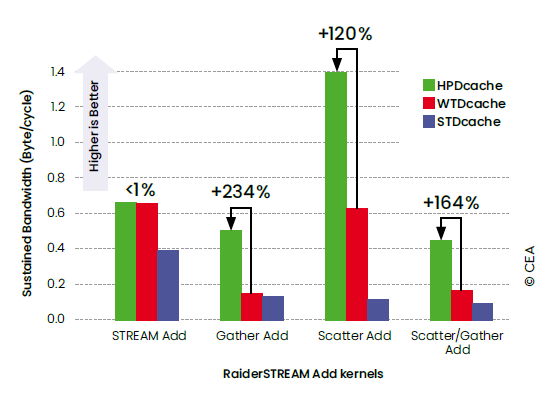

This advance is available through the OpenHW Group’s IP catalog, where it can be accessed on an open-source basis by the broader development and engineering communities. Currently, it is used with the 64-bit RISC-V open-source CVA6 core suitable for a wide range of HPC and AI applications— widely used in Europe. In tests, the cache was up to 3.3 times faster than caches previously used with CVA6, resulting in a significant performance improvement. HPDcache’s commercial-grade quality is guaranteed by a comprehensive testing protocol and a UVM test bench. These tools can be used to test and validate cache performance and reliability for industrial use cases. Rigorous testing is crucial to ensuring that HPDcache is reliable in production environments. As part of the European Processor Initiative (EPI), HPDcache has been integrated into EPAC and RHEA, two silicon ICs with integrated VRP/VxP accelerators, demonstrating that HPDcache is mature and ready for industrial deployment.

By offering innovative solutions to latency and memory bandwidth, HPDcache represents a major breakthrough in HPC and AI. Open-source releases of the IP and test bench have positioned the CEA to join projects like the EU TRISTAN project to make RISC-V-based solutions more readily available and has led to research partnerships through the OpenHW Group for the RISC-V CVA6 ecosystem.

Several European stakeholders, including Bosch and Thales, are using CVA6 with HPDcache for their automotive processors and embedded systems. In addition, HPDcache is used in the basic configuration of CVA6. The Barcelona Supercomputing Center has integrated HPDcache with high-performance RISC-V processors developed in-house. The goal is to use them in the next generation of Marenostrum supercomputers.