Afin d’obtenir des accélérations grâce aux QPUs, il faut pouvoir convertir les problèmes d’intérêt en une série d’instructions (requêtes ou queries) pouvant être traitées par la puce quantique. Ce formatage du problème en requêtes est un goulet d’étranglement pour de nombreuses applications qui peut mitiger voire annuler les gains potentiels des algorithmes quantiques. Un des axes de recherche structurant au sein de l’équipe consiste à proposer des stratégies permettant de formater les problèmes liés à la préparation et l’utilisation des données pour le calcul sur QPU. Cela a donné lieu à deux publications.

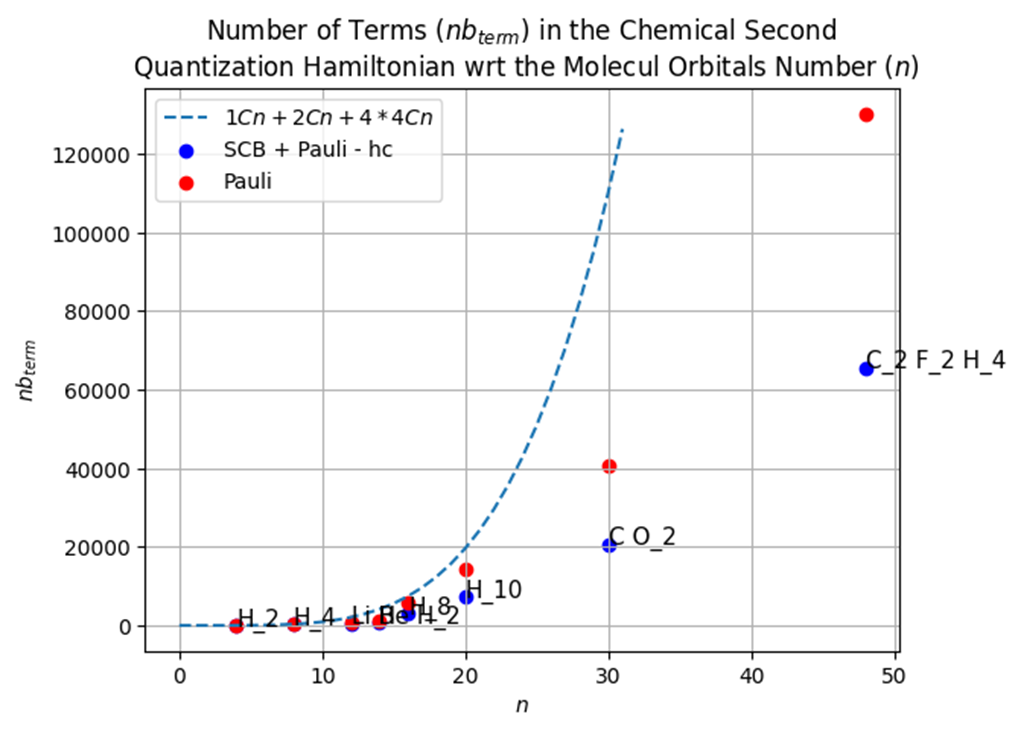

1. Pour les QPUs à portes : dans ce modèle, la requête se présente sous la forme d’une matrice contenant les données du problème. Cette matrice doit s’exprimer en un produit du plus petit nombre possible de portes quantiques élémentaires. Les travaux de l’équipe portent sur les décompositions efficaces pour des matrices liées à des applications. Cette année, une publication[1] à IPDPS porte sur l’amélioration des implémentations de nombreuses matrices. Un code automatisant les techniques proposées dans cet article a fait l’objet d’un dépôt APP.

2. Pour les QPU en temps continu parfois appelés analogiques ou simulateurs quantiques : ces machines sont capables de traiter tout problème qui possède une réduction vers un problème d’optimisation binaire quadratique non contraint (QUBO). Dans ce cadre, l’équipe propose des réductions efficaces pour des problèmes associés à des applications. Cette démarche a conduit à une nouvelle réduction pour la résolution de systèmes linéaires, ce qui a donné lieu à une proposition de brevet.

Un autre champ explore les heuristiques d’optimisation quantiques et leur benchmarking. Celui-ci est particulièrement pertinent, car contrairement aux benchmarks basés sur la qualité des opérations quantiques, il permet de comparer les performances des processeurs quantiques avec celles des autres types de processeurs.

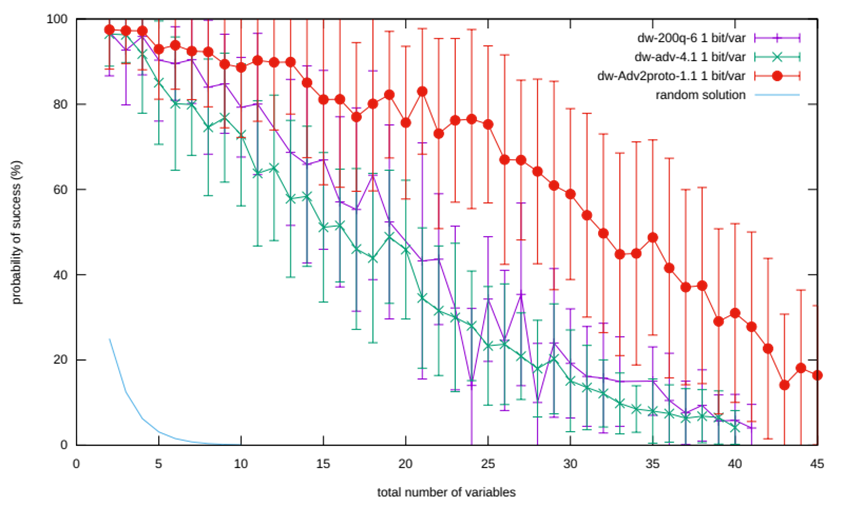

De par leur maturité technologique, les travaux de benchmark de l’équipe se sont d’abord portés sur les QPUs à recuit quantique (quantum annealer, QA) Dwave et une heuristique « quantum inspired » Vector Annealing (VA) de NEC. Cela permet de réaliser des comparaisons de performance par rapport à des heuristiques classiques ou entre heuristiques quantiques. Cela c’est aussi traduit par une publication[2] à QCE dans laquelle un premier test de performance d’heuristique sur problème contraint a permis de comparer QA et VA.

Ces travaux sur les annealers s’inscrivent dans les missions confiées au CEA dans le cadre du projet BACQ (MetriQs / France-2030). Il se poursuivront prochainement par l’utilisation des machines quantiques Ruby et Lucy installées au TGCC. L’expertise gagnée sur les annealers quantiques permet aussi d’être reconnu pour des sessions d’écoles d’été (EDF-CEA-INRIA) ou d’hiver (Riken) ainsi que de tutoriels (Hub quantique).

Bien que les ordinateurs quantiques (QPUs) soient encore à bas TRL, les premiers benchmarks montrent les progrès importants visibles entre les générations successives de QPUs.

Benchmarking des ordinateurs quantiques, BACQ : si vous ne pouvez pas le mesurer, vous ne pouvez pas l’améliorer. (Lord Kelvin)