Weebit Nano est une jeune société israélienne qui adresse le marché des mémoires innovantes. Elle a souhaité que le CEA conçoive un démonstrateur complet pour promouvoir sa technologie brevetée de mémoire non volatile embarquée (eNVM). Ce démonstrateur a permis à Weebit Nano de vendre/licencier sa technologie à des fondeurs américains et asiatiques. A l’origine, Weebit Nano est venu prospecter auprès du CEA du fait de ses expertises en technologie eNVM, en conception de circuits et de systèmes, et en test de circuits sur wafer ou en package.

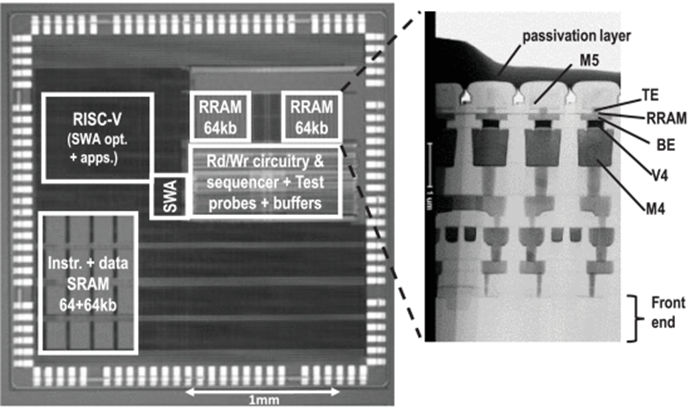

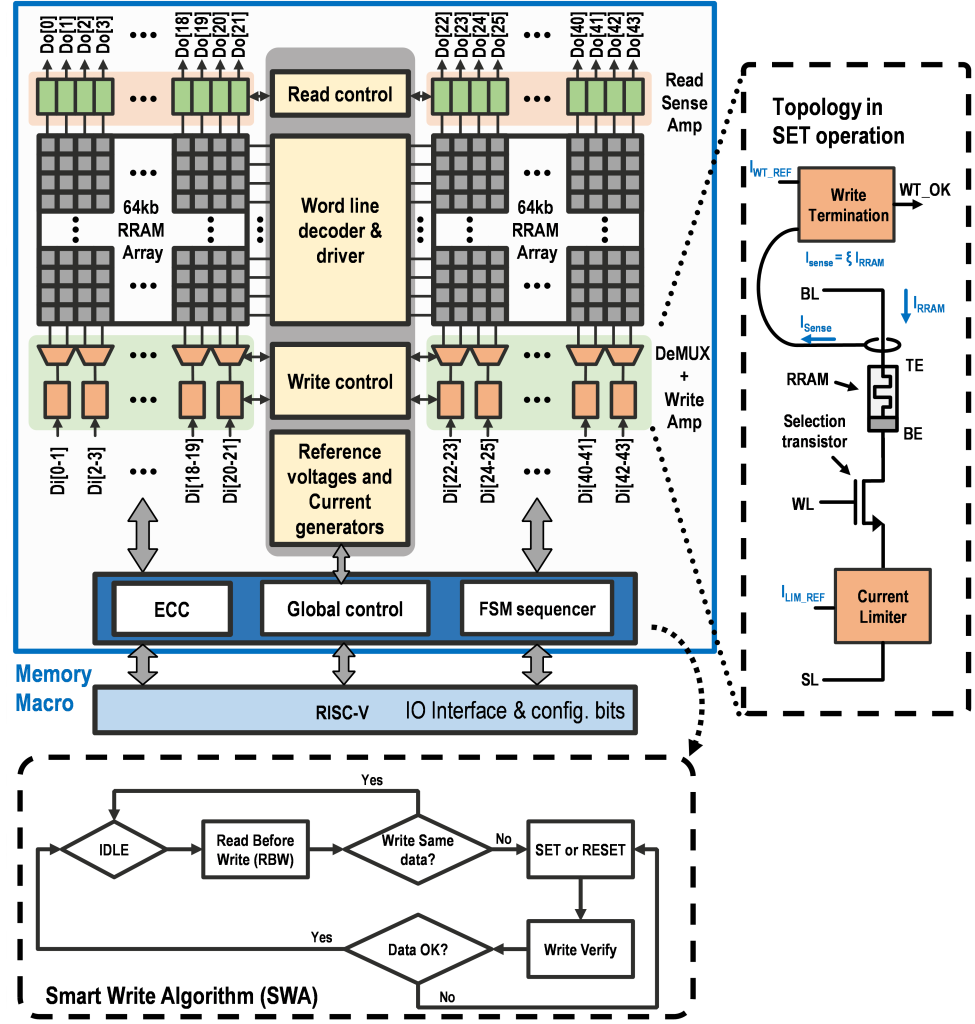

Ce démonstrateur inclut une macro mémoire non volatile, ainsi que des circuits analogiques fournissant les signaux précis, mais aussi ajustables, nécessaires à l’écriture et la lecture complexes de ce type de mémoire (Fig. 1). Il comprend aussi des circuits de contrôle à base de sous-système RISC-V mais aussi d’un contrôleur dédié développé spécifiquement pour ce projet.

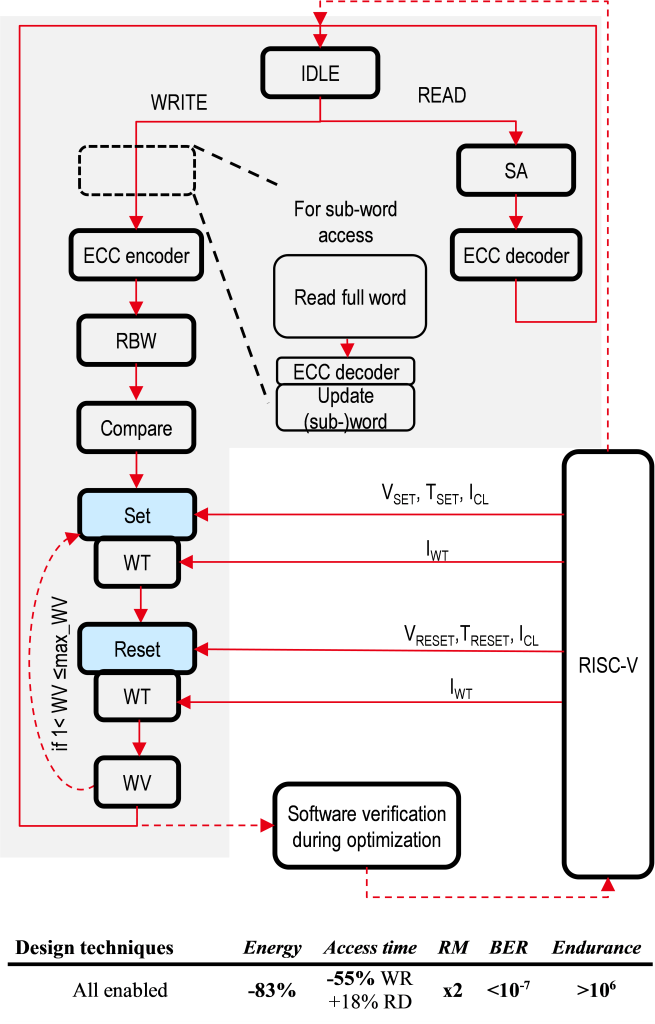

* le fait de lire la valeur binaire d’une cellule mémoire avant écriture et de ne réaliser l’écriture qu’à condition que le bit ne soit pas dans l’état désiré,

* le fait de vérifier l’état de la cellule écrite après écriture et recommencer l’écriture jusqu’à que l’opération d’écriture soit correcte.

* l’ECC, qui détecte ou/et corrige un mot lu en se servant de bits codant la parité de sous-groupes du mot.

Ces travaux, et notamment les optimisations obtenues à partir du SWA, ont mené à des améliorations significatives (Fig. 2 et principale), à température ambiante, de :

Toutes ces réussites positionnent la technologie RRAM développée en partenariat avec Weebit Nano comme un candidat prometteur pour une adoption industrielle massive.

Projet stimulant ayant permis la collaboration de 7 laboratoires du CEA allant de la technologie à la conception de circuits avec le test de système sur puce, afin de concevoir la 1ère NVM du CEA.

Nous sommes extrêmement satisfaits du travail de l’équipe... Respect du calendrier pour la mise en production, adaptation aux demandes de modification de Weebit, mise en oeuvre de plusieurs modes de test et conception flexible, une disposition extrêmement claire.

Amélioration du produit énergie délais de 15x.