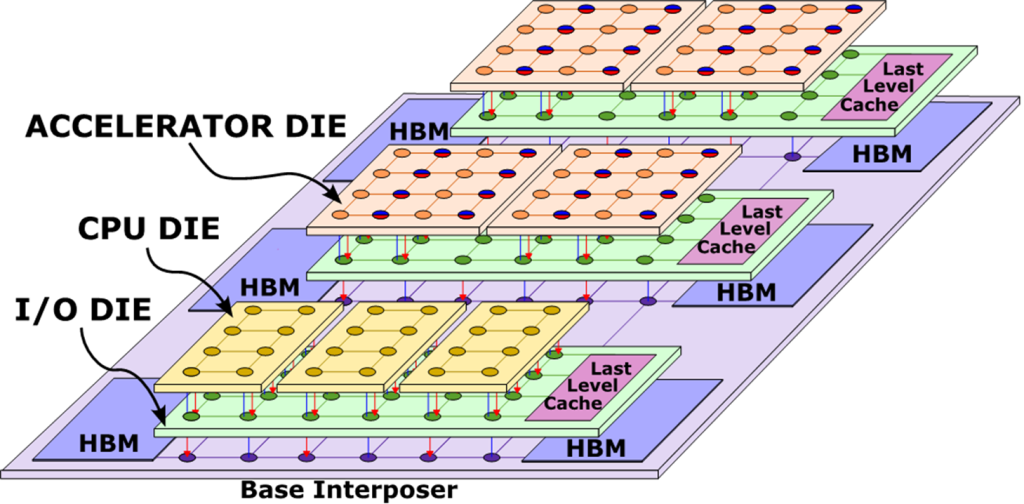

La technologie 3.5D (parfois appelée 5.5D) révolutionne l’architecture des circuits en empilant plusieurs chiplets sur un interposeur, formant des structures verticales comparables aux gratte-ciels de Manhattan. Pour assurer la communication entre les différents nœuds de calcul – processeurs, GPUs ou accélérateurs –, des réseaux sur puce (NoCs) sont basés sur des protocoles de routage permettant à des éléments de données (flits) de circuler d’une source à une destination. Si les algorithmes de routage pour les topologies planaires ou 2.5D (plusieurs chiplets directement empilés sur un interposeur) sont bien établis, la 3.5D introduit une complexité supplémentaire : les flits peuvent à présent réaliser plusieurs transitions verticales entre les chiplets pour atteindre leurs destinations, nécessitant des solutions innovantes. Davy Million, lauréat d’une bourse Fulbright, a développé dans le cadre de sa thèse en partenariat avec l’Université de Californie à Santa Barbara l’algorithme Depth-First [2], spécialement conçu pour les architectures 3.5D. Ce protocole garantit un acheminement efficace des données tout en évitant les dead-locks, des dépendances circulaires entre les ressources du réseau qui sont susceptibles de le paralyser. Une avancée majeure pour les circuits 3.5D.

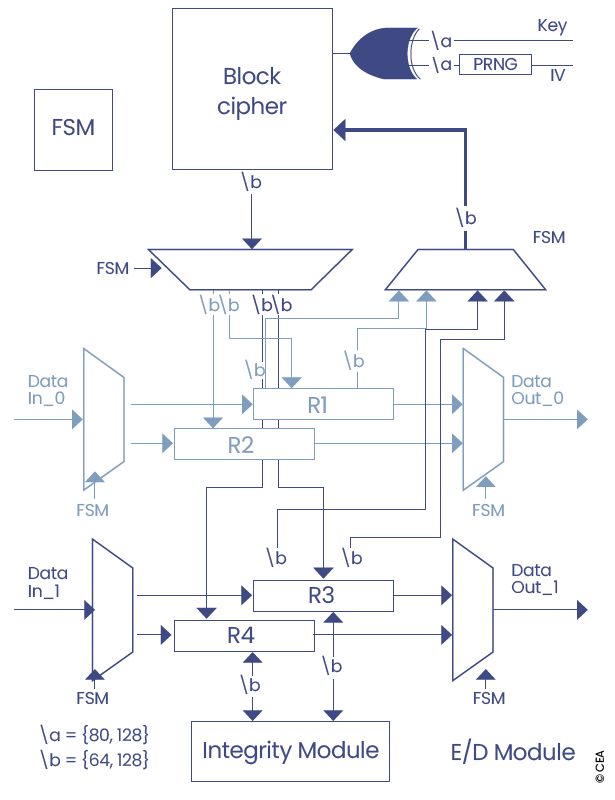

Dans les systèmes multi-puce, les différents chiplets, qui peuvent provenir de fonderies distinctes, sont testés par des acteurs tiers et assemblés par d’autres entreprises, formant un écosystème complexe. Cette fragmentation impose de garantir l’authenticité de chaque puce pour prévenir l’intégration de chiplets contrefaits ou malveillants, ainsi que l’exfiltration de données sensibles via les ports de test. Pour répondre à ces enjeux, Juan SUZANO, dans le cadre d’une thèse CIFRE avec STMicroelectronics et le laboratoire TIMA, a développé une solution innovante combinant authentification des chiplets et chiffrement des données de test. Son approche, compatible avec les standards IEEE 1686 et 1838 et conçue pour une adoption industrielle, a été publiée dans le Journal JETCAS [3]. Elle constitue une réponse concrète aux vulnérabilités de sécurité des architectures à chiplets, favorisant ainsi le développement d’un écosystème ouvert et sécurisé.

L’intégration en 3D est devenue un aspect central de l’architecture des systèmes haute performance…

Le marché des chiplets et circuits 3D croit à 24 %/an et vaudra 157 milliards $ en 2030.

Simulateur de Noc 3.5D disponible sur le github du CEA-List : https://github.com/CEA-LIST/Noxim-3.5D

[1] P. Vivet et al., « IntAct: A 96-Core Processor With Six Chiplets 3D-Stacked on an Active Interposer With Distributed Interconnects and Integrated Power Management, » in IEEE JSSC, vol. 56, no. 1, pp. 79-97, Jan. 2021. (https://doi.org/10.1109/JSSC.2020.3036341)

[2] D. Million et al., « Depth-First: A Deterministic and Scalable NoC Routing Protocol for 3.5D Packaged Architectures, » IEEE JETCAS 2025. (https://doi.org/10.1109/JETCAS.2025.3590106)

[3] J. Suzano, et al, « Enhancing DFT Security in Chiplet-Based Systems With Encryption and Integrity Checking, » in IEEE JETCAS 2025. (https://doi.org/10.1109/JETCAS.2025.3592984)