Les ordinateurs quantiques, susceptibles de révolutionner la médecine, les matériaux et l’intelligence artificielle, menacent la sécurité des communications. Les systèmes cryptographiques comme RSA, Diffie-Hellman et ECC sont vulnérables aux attaques quantiques, ce qui motive le développement de la cryptographie post-quantique (PQC). HQC, un schéma fondé sur un formalisme mathématique dérivé de la théorie des codes et sélectionné comme standard par le NIST en 2025, présente des performances relativement faibles par rapport aux autres candidats, basés sur des réseaux euclidiens. Bien que plus rapides, les implémentations matérielles sont coûteuses en surface silicium, la multiplication polynomiale sur de polynômes de très grande taille constituant le principal goulot d’étranglement.

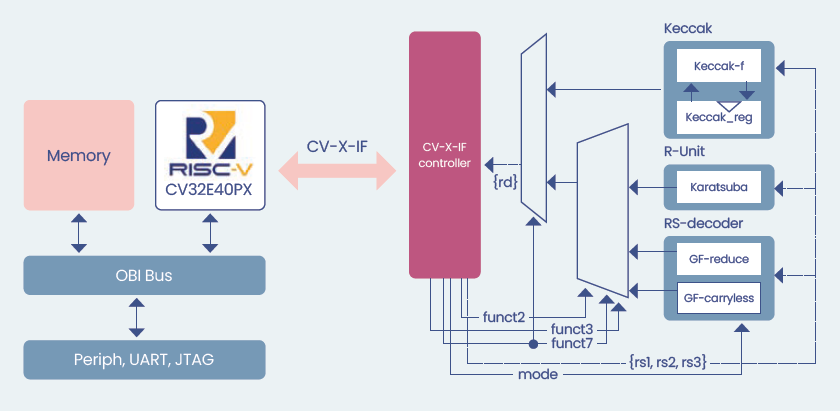

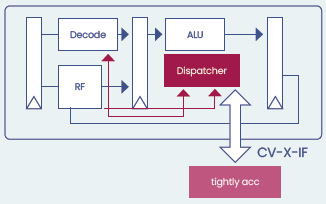

Une alternative aux méthodes classiques d’accélération matérielle est l’accélération étroitement couplée, qui encapsule les opérations récurrentes de l’algorithme dans des instructions personnalisées ajoutées au jeu d’instruction du processeur. Grâce à l’interface Core-V eXtension (CV-X-IF), l’accélérateur s’intègre parfaitement dans le pipeline d’exécution des processeurs RISC-V, offrant un gain de vitesse transparent tout en surmontant les défis traditionnels d’extension de l’ISA.

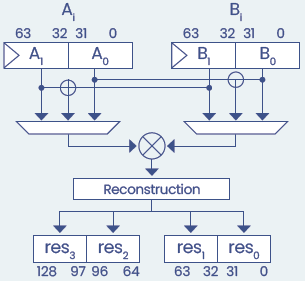

Nous avons appliqué cette nouvelle stratégie d’accélération étroitement couplée et conçu trois blocs d’accélération matérielle dédiés ciblant les principaux goulots d’étranglement de l’algorithme HQC. La R-Unit accélère la multiplication polynomiale via une approche Karatsuba en plusieurs étapes sur des blocs de 32 bits avec quatre instructions personnalisées pour gérer complètement le résultat. Le RS-Decoder accélère les opérations clés sur les champs de Galois, dont la multiplication sans retenue et le comptage des zéros finaux, grâce à plusieurs instructions spécialisées éliminant boucles et résultats intermédiaires.

Enfin, l’accélérateur Keccak gère l’état de permutation de 1600 bits avec un registre dédié et trois instructions personnalisées pour un chargement, un traitement et un stockage efficaces, minimisant les surcoûts par rapport aux approches classiques faiblement couplées.

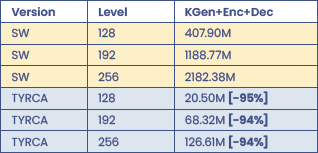

En appliquant cette stratégie d’accélération étroitement couplée, TYRCA montre des améliorations de performance par rapport à l’implémentation logicielle originale de HQC.

À tous les niveaux de sécurité (HQC-128/192/256), les opérations de génération de clé (KeyGen), d’encapsulation et décapsulation (Encaps, Decaps) voient une réduction d’environ 95 % du nombre de cycles d’horloge. L’utilisation de la mémoire d’instructions est également fortement réduite. Implémenté sur une cible FPGA Kintex-7, TYRCA occupe moins de 26 % de la surface totale du système sur-puce, le R-Unit fournissant le gain de performance le plus élevé tout en utilisant moins de 10 % de cette surface.

Les métriques de vitesse normalisées (vitesse/surface) confirment que TYRCA surpasse les approches faiblement couplées précédentes.