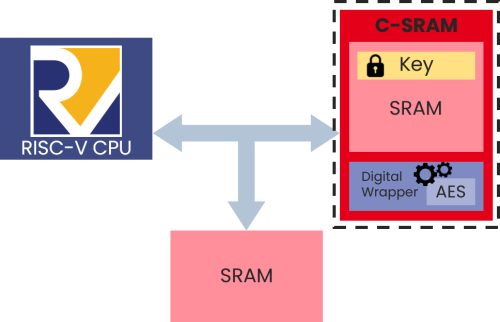

Les travaux réalisés visent à exploiter la confidentialité du calcul proche mémoire dans le cadre d’opérations de chiffrement de données. Une IP C-SRAM (Computational SRAM) a été implémentée puis intégrée dans un système embarqué sur cible ASIC, circuit VASCO-2, (cf. figure 1). Ce système combine un cœur RISC-V 32-bits ainsi que ses mémoires à cet accélérateur matériel C-SRAM permettant à la fois le stockage de données et la réalisation de calculs en son sein.

L’algorithme de chiffrement AES a été porté en utilisant le calcul proche mémoire de la C-SRAM. Cette version accélérée matériellement peut ainsi être comparée à une version purement logicielle exécutée par le cœur RISC-V. Par ailleurs, la C-SRAM intègre une fonctionnalité de génération de clés secrètes « in-situ» (basée sur la technologie PUF).

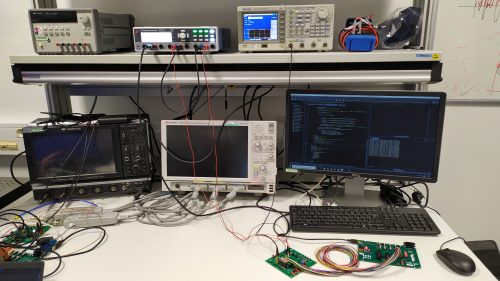

Un ASIC a été fondu en 2022 en technologie 22nm FD-SOI de GlobalFoundries. Ce circuit et la carte de test associée ont permis de vérifier le fonctionnement de l’IP C-SRAM et de réaliser des mesures précises sur silicium (grâce à l’implémentation de grilles d’alimentation séparées pour les régions matrice/ périphérique/logique de la C-SRAM) :

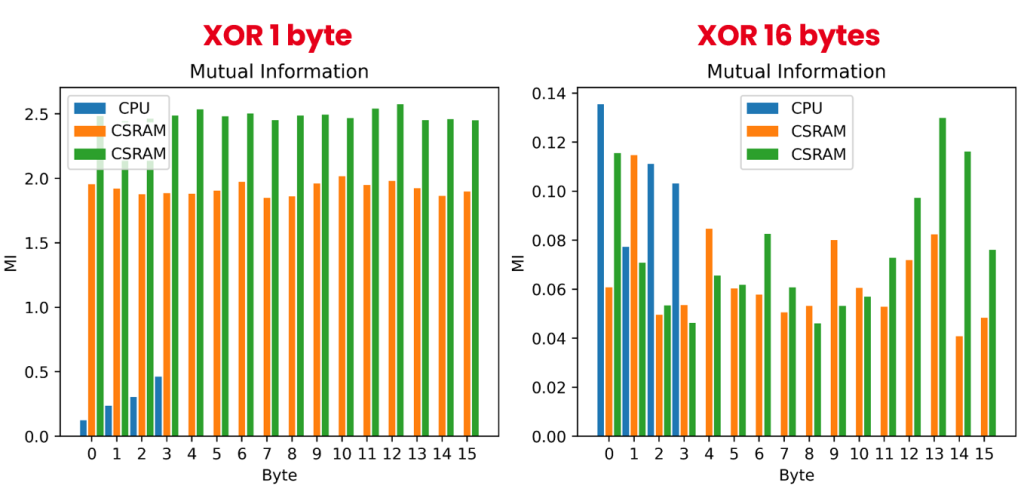

L’analyse de l’information mutuelle d’un calcul parallélisé 128 bits sur C-SRAM ouvre des perspectives en termes de sécurité, notamment pour l’accélération de la PQC sur C-SRAM (figure 4).

Le parallélisme offert par la C-SRAM, peut être exploité pour effectivement réduire les fuites de l’architecture. La diminution des fuites due à la réduction de transfert des données dans le bus d’interconnexion sera évaluée expérimentalement dans des travaux futurs.

Cas d’usage :

Projet majeur :

Projet d’envergure mettant en avant les innovations de différents laboratoires du CEA dans le domaine de la cybersécurité matérielle/ logicielle avec caractérisation et démonstration sur cible ASIC.