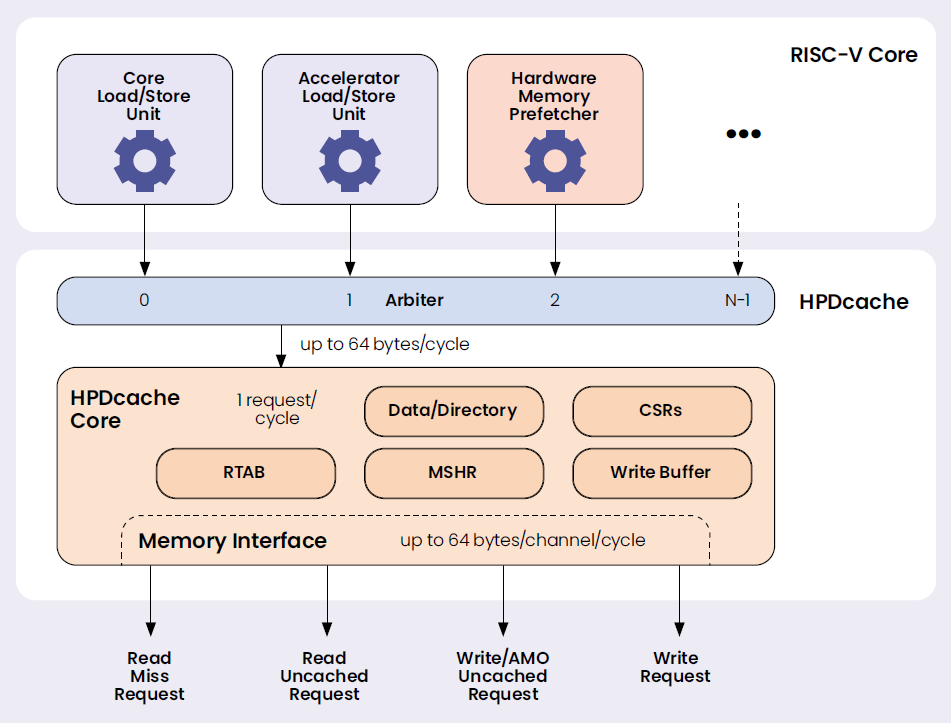

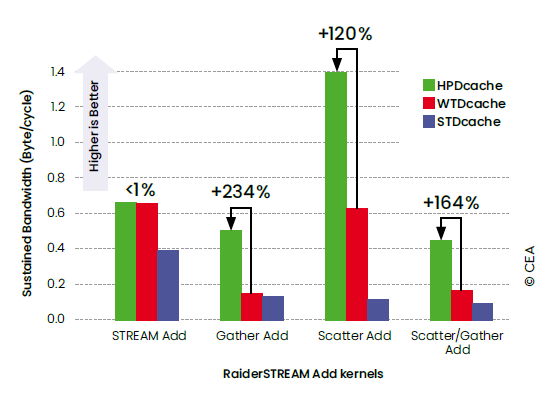

Dans ces domaines, les applications utilisent une quantité croissante de données et réalisent des motifs d’accès mémoire irréguliers. Ces motifs d’accès diminuent l’efficacité des mémoires caches, ce qui constitue un défi important pour l’optimisation des performances. Le HPDcache a été conçu pour pallier ce problème, en permettant l’exécution simultanée de plusieurs requêtes mémoire. Cette approche permet de masquer la latence d’accès mémoire et fournit une bande passante élevée, améliorant ainsi les performances globales des systèmes.

Le HPDcache a été mis en open source via le catalogue d’IP de l’OpenHW Group, ce qui le rend accessible à une large communauté de développeurs et d’ingénieurs. Il est actuellement utilisé avec le coeur CVA6, un coeur open source RISC-V 64-bits largement adopté en Europe pour ses applications variées telles que le HPC et l’intelligence artificielle. Les tests ont montré un facteur d’accélération allant jusqu’à 3.3x par rapport aux caches précédemment utilisés avec le CVA6, menant à une amélioration significative des performances. La qualité industrielle du HPDcache est assurée par le plan de test complet et un « testbench UVM ». Ces outils permettent de vérifier et de valider les performances et la fiabilité du cache, garantissant ainsi qu’il répond aux exigences des applications industrielles. Cette approche rigoureuse en matière de tests est essentielle pour garantir que le HPDcache fonctionne de manière fiable dans des environnements de production. Le HPDcache a été intégré dans des circuits intégrant l’accélérateur VRP/VxP dans deux circuits (EPAC et RHEA) de l’European Processor Initiative (EPI). Cette intégration sur silicium démontre la maturité et la robustesse du HPDcache, le rendant prêt pour une utilisation industrielle.

En résumé, le HPDcache représente une avancée majeure dans les domaines du HPC et de l’intelligence artificielle, offrant des solutions innovantes pour surmonter les défis de la latence et de la bande passante mémoire.

Les mises en open-source de cette IP et de son « testbench » ont permis au CEA d’intégrer des projets collaboratifs tels que le projet européen TRISTAN qui vise la diffusion des solutions à base de RISC-V. Cette initiative apporte des collaborations de recherche, en particulier par l’intermédiaire de l’Open Hardware Group pour l’écosystème RISC-V CVA6.

Plusieurs acteurs européens, dont Bosch et Thales, utilisent le couple CVA6-HPDcache pour leurs processeurs automobiles et systèmes embarqués. Le HPDcache est d’ailleurs utilisé dans la configuration de base du CVA6. Le BSC a intégré le HPDcache avec des processeurs RISC-V haute performance, développés en interne, avec l’objectif qu’ils fassent partie de la prochaine génération de supercalculateurs Marenostrum.

“HPDcache: Open-Source High Performance L1 Data Cache for RISC-V Cores” Cesar Fuguet (2023) 10.1145/3587135.3591413, Conférence CF-OSHW