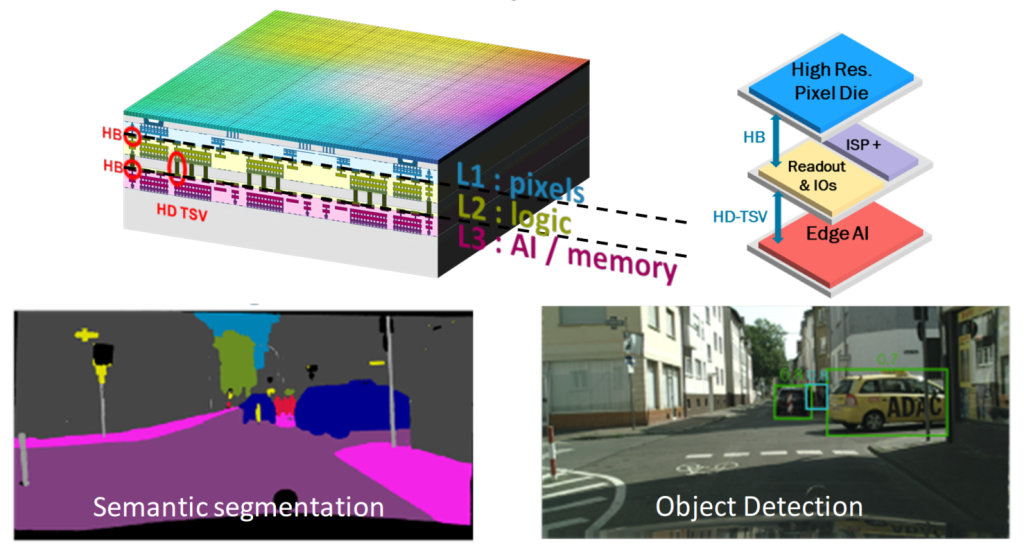

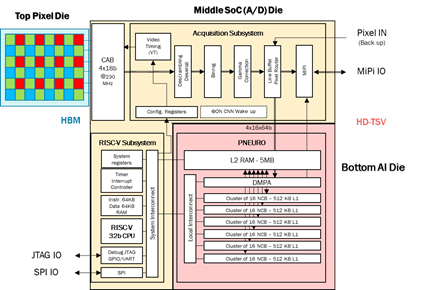

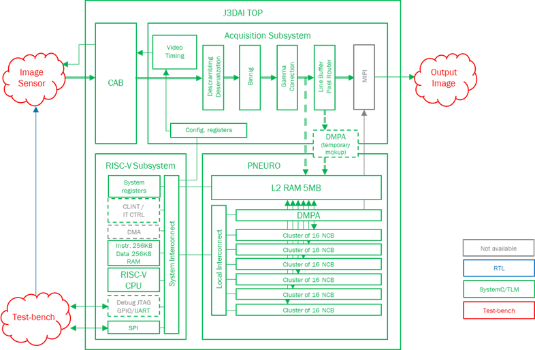

L’architecture du démonstrateur d’imageur intelligent 3-couches nommé J3DAI étudié dans le programme IRT Smart Imager s’appuie sur l’accélérateur hardware PNeuro du CEA-List, qui permet l’inférence de multiples réseaux IA à la dimension du capteur d’image.

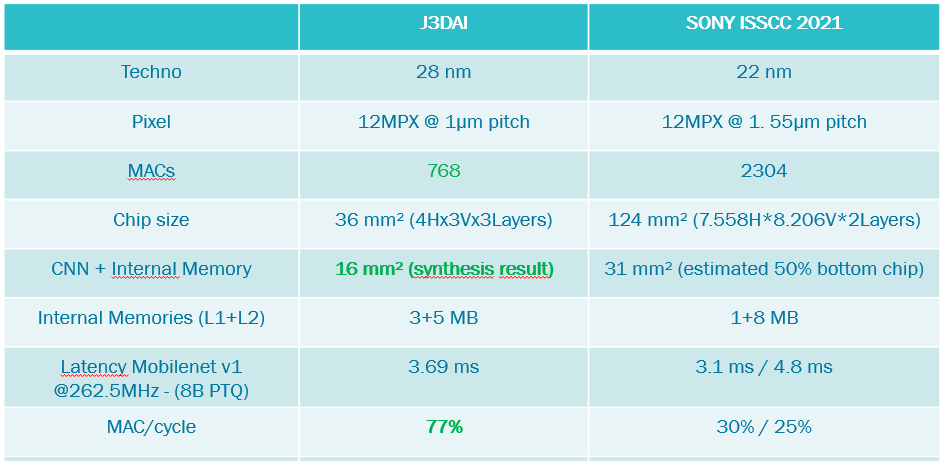

L’architecture de cet imageur est visible en figure 1. Des simulations réalisées sur un réseau de type Mobilenet V1 ont permis de montrer que cette architecture présente une consommation de 50 mW dans le cas d’un flux vidéo de 30 images par secondes. De plus, une comparaison de performances et de surface avec l’imageur IA de Sony publié en 2021 à la conférence ISSCC montre un temps d’exécution similaire (3,69 ms vs 3,1 ms) mais avec trois fois moins d’unités de calcul MAC (Multiply ACcumulate), 768 vs 2304, et trois fois moins de surface silicium (36 mm² vs 124 mm²) comme le montre le tableau de la figure 2.

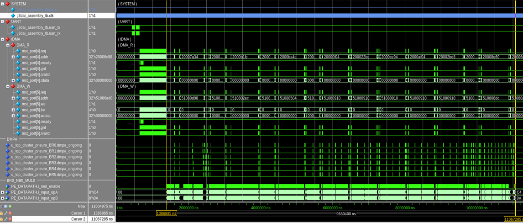

En parallèle, une plateforme virtuelle (Figure 4), s’appuyant sur les outils CAD SIEMENS a été développée. Cette plateforme basée sur un système PNeuro associé à un processeur de type RISC-V (32 bits) permet une simulation grandement accélérée (x2 000 : 13 secondes vs. 7h et 45 minutes) de tâches complexes tout en garantissant un résultat équivalent à la simulation bas niveau.

Avec un ralentissement notable du marché dans le secteur des smartphones, les imageurs s’adaptent aux besoins des marchés, où de nouvelles opportunités se présentent dans les domaines de l’automobile, de l’industrie et de la sécurité. Les approches développées dans le programme Smart Imager, basées sur les technologies d’empilement 3D multicouches, avec introduction d’intelligence artificielle au sein même du capteur, répondent parfaitement aux enjeux des marchés actuels et à venir, dans lesquels évoluent les partenaires industriels du programme.

Gain en efficacité MAC et surface silicium

Imageur intelligent pour analyse intensive d’images en temps réel