Les attaques par injection de fautes exploitent des conditions anormales (température, rayonnement, etc.) pour perturber un système embarqué. Elles induisent des erreurs qui permettent à un attaquant d’accéder à des données sensibles ou d’acquérir des privilèges. Un composant clé dans la sécurité des systèmes sur puce (SoC) est son sous-système sécurisé, ou secure element (SE). Traditionnellement, l’analyse de la robustesse d’un SE repose sur une caractérisation post-silicum coûteuse et aux résultats souvent variables (évaluateur, outils, etc.).

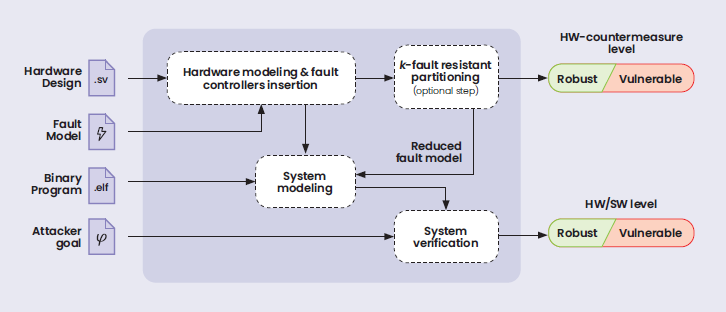

Face au coût et au temps que représente le processus de certification de sécurité d’un produit, il est nécessaire de développer des méthodologies pré-silicium d’analyse pour évaluer les capacités de contre-mesures logicielles et/ou matérielles présentes pour sécuriser un SE. μArchiFI, développé par le CEA-List, est un tel outil d’analyse pré-silicium, à l’état de l’art, permettant d’évaluer la robustesse d’un SE face à des attaques par injection de fautes. Il analyse la description d’un circuit au niveau Register Transfer Level (RTL), un modèle de fautes, un programme et un objectif d’attaque, afin d’identifier les vulnérabilités ou démontrer formellement la robustesse du système. Jusqu’ici, μArchiFI supportait un modèle de faute restreint et une taille de code analysable d’une centaine d’instructions. Ces limitations empêchaient l’analyse du code de démarrage d’un SE face à une attaque par injection de fautes.

Nos méthodologies d’analyse se sont enrichies d’une approche dite k-fault resistant partitioning (k-FRP), développée en partenariat avec l’Université Technique de Graz (TU Graz). Cette collaboration a permis une première mondiale : une analyse sécuritaire d’OpenTitan contre les attaques par injection de fautes. OpenTitan est le premier SE open-source développé par un consortium d’acteurs de premier plan des systèmes numériques et de la cyber-sécurité.

Le k-FRP (à terme étape optionnelle sur le workflow de μArchiFI ci-dessous) a notamment permis de :

Enfin, cette analyse a permis de démontrer que la seule vulnérabilité identifiée par le k-FRP n’était pas exploitable dans les 2 500 instructions du premier étage de code de démarrage d’OpenTitan. L’analyse de sécurité de ce type de systèmes (sécurisés avec des contre-mesures matérielles de type redondance matérielle), pour ce modèle d’attaquant d’injection de fautes, était auparavant impossible à réaliser.

Nos méthodologies d’analyse pré-silicium, intégrant les vulnérabilités micro-architecturales, sont centrales dans les projets Forward (recherche partenariale PTCC) et TwinSec (Recherche à Risque, programme Audace du CEA) démarrés fin 2024. Ces projets permettront aussi bien de comparer les résultats obtenus par rapport à des caractérisations sécuritaires expérimentales que de concevoir une chaîne d’analyse multi-niveaux (physique, micro-architectural et logiciel) intégrant nos méthodologies pré-silicium. Les travaux menés dans les deux projets visent notamment des modèles multi-fautes réalistes et des processeurs de complexité accrue.

La conférence CHES 2024 (rang A*) est une des principales conférences internationales dans le domaine de la sécurité.

Plusieurs industriels et l’ANSSI se sont montrés intéressés par nos méthodologies d’analyse. Par exemple, l’ANSSI évalue l’usage de méthodes formelles dans le cadre de ses analyses sécuritaires architecture du composant de sécurité OpenTitan.

Liens vers nos méthodologies d’analyses μArchiFI et k-fault resistant partitioning